សេចក្តីថ្លែងការណ៍សិទ្ធិឯកជន: ភាពឯកជនរបស់អ្នកមានសារៈសំខាន់ណាស់សម្រាប់យើង។ ក្រុមហ៊ុនរបស់យើងសន្យាថានឹងមិនបង្ហាញព័ត៌មានផ្ទាល់ខ្លួនរបស់អ្នកទៅប្រទេសនីន្នីណាមួយដែលមានការអនុញ្ញាតច្បាស់លាស់របស់អ្នកឡើយ។

+86-0510-86199063

1 Introduction

In August of this year, a group of high-performance and representative humanized air conditioners represented by Gree's “sleeping treasure” bedroom air conditioners attracted a large number of consumers' attention, but their high prices also made many ordinary ones. Consumers are discouraged.

In addition to the profit-based considerations of merchants, the high price of the air-conditioning market is a very important reason for the huge investment in the research and development of air-conditioning. Taking Galanz as an example, the company's annual research and development fund is as high as 10 million yuan, and it is not difficult to imagine the huge amount of R&D expenditure. How to reduce design costs, shorten the research and development cycle, and avoid the early stage of venture capital has become an important issue facing the development of the air-conditioning industry.

Based on the consideration of the above problems, this paper takes the design of a small multi-function household air conditioner controller as an example to introduce an FPGA solution with simple design, excellent performance and effective cost control.

2 Design indicators

The task of this design is a small home air conditioning controller with multiple operating modes and multiple wind speeds to choose from. The basic design indicators are as follows:

1. After the system is powered on, it defaults to the standard mode, the wind speed is level 1, the self-set temperature is 22 °C, the timing function is off, and the working status indicator is on.

2. The system has four working modes:

Standard mode: The system compares the user's own temperature with the room temperature to drive the response device to work.

Automatic mode: the system is based on the indoor temperature and the preset temperature in the system.

The threshold is compared and judged to drive the response device to work.

Sleep mode: In addition to the function with standard mode, the system can automatically adjust the temperature according to the characteristics of human sleep and night temperature changes.

Dehumidification mode: When this mode is enabled, the response device will be driven to dehumidify the room.

3. In addition, the system also provides four levels of wind speed for users to choose, convenient temperature setting input, timing, working status indication and other functions.

3 introduction of FPGA solutions

For a long time, the design of such household air-conditioning controllers is mostly realized by a single-chip microcomputer, which is characterized by low cost and general performance. However, the integration of ordinary single-chip microcomputers is usually low. For example, Intel's AT89S51 only has 128 bytes of on-chip data memory, 32 programmable I/O lines, and 5 interrupt sources. Obviously, in order to complete more complex operations and control functions, it must be extended, and the delay caused by external hardware circuits and other unpredictable risks, so that the expansion must be at the expense of the performance of the whole machine. Moreover, this design method is subject to hardware circuits and is difficult to develop. The air-conditioning special chips developed by some merchants are also due to technical barriers and have no advantages in terms of versatility, upgrade and price.

As an emerging programmable technology, FPGA is the ideal carrier for prototyping. Its accurate testability and deep sub-micron process that has been achieved can better solve many problems in traditional design methods. Its rich programming resources and flexible programming features can transform many functions that would otherwise need to be implemented by external hardware into software programming, making upgrade improvements more flexible. Moreover, this design method can accurately predict and estimate the design in the software stage, which can greatly improve the development efficiency and effectively avoid the previous venture capital. Modern advanced FPGA technology has greatly reduced the power consumption and price of the FPGA. Taking the EPCS1SI8 chip with a working voltage of 3.3V as an example, its current market price is only about 10 yuan.

4 system division

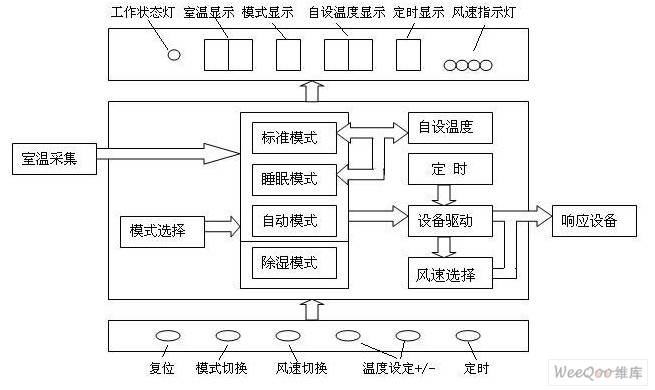

One of the great advantages of FPGA technology is the use of top-down design ideas to modularize the design. To complete the various functions of the controller, the design is divided into multiple modules. The composition of the entire controller and the control relationship between the modules are shown in Figure 1.

Figure 1 Controller structure diagram

It can be seen from Fig. 1 that the controller is composed of working mode (including mode selection and four working modes), wind speed selection, room temperature setting, timing, device driving and the like. And there is a clear control relationship between the modules.

5 design implementation

It can be known from the system division that the functions of the controller are coordinated by each module. Among them, the mode selection, room temperature setting, timing three modules must accept the input from the outside, through the hardware measurement, the design selects the system frequency of 4HZ to reduce the jitter interference during the key input process. In addition, the finite state machine design is an important way to carry out high efficiency and high reliability logic control [3], and this design method has been used many times in the design. The design ideas and workflows of the control relationships between modules and modules are explained below.

5.1 Working mode

The mode selection consists of a selection control and four operating modes.

Select Control: This module provides strobe signals for the four working modes, and starts cyclic switching from NORMAL by pressing the button to drive each mode to work normally. This part is designed as a character finite state machine with four working states, and its state transition control relationship is shown in Fig. 2.

Figure 2 Select control state transition diagram

Standard mode: The module compares the externally collected room temperature with the user-set temperature value to determine the current room temperature condition (cold, hot or suitable) and sends the status information to the drive module for processing.

Auto mode: This module compares the externally collected room temperature with the preset temperature threshold in the system (here set to [17°C-26°C]). If the externally collected temperature exceeds the threshold, there is a corresponding status signal. The drive module is issued.

Sleep mode: In addition to the standard mode function, in order to create a comfortable sleeping environment, the system will send a request signal of 1 °C to the self-designed temperature module every hour, and send it to the device driver module after 5 hours. Shutdown request. The sleep mode programming flow is shown in Figure 3.

Figure 3 sleep mode design flow chart

Dehumidification mode: In this mode, the dehumidification request is automatically sent to the device driver module.

5. 2 Wind speed selection

The wind speed selection module is provided with a strobe signal by the device driver. This part is realized by a character finite state machine with five working states, and cyclically switches from ST0 to ST3 by pressing a button. When the device driver module has no device request output, the wind speed automatically switches to the ST4 state, prohibiting the fan from working; when the device driver resumes the device request, the wind speed will be switched back to the original state. The wind speed selection module state transition control relationship is shown in Figure 4.

Figure 4 Wind speed switching state transition diagram

5.3 Timing

In this module, the shutdown time is preset by the button (up to 270 minutes), and the shutdown time is sent to the real-time display. When the system is turned off, the system status indicator will be flashed. In order to facilitate user input, save the keys and display the hardware resources used, the program adopts the design method of mapping input and mapping display, which means that the user replaces the program with a specific step value (here set to 30min) each time, and will The countdown reverses the output display by the step interval. The part of the programming process is shown in Figure 5.

Figure 5 timing module design flow chart

5.4 Room temperature setting

The room temperature setting module is input by a pair of addition and subtraction button cycles, and also receives the temperature adjustment request from the sleep module, and the temperature adjustable interval is set to [10 ° C - 35 ° C]. In the program design, the VHDL incomplete IF statement maintains the original value, and the self-set temperature increase and decrease function can be easily realized. The module can be set only when the system is operating in standard mode or sleep mode, and the rest is reset to an initial value of 22 °C.

5.5 device driver

The device driver module receives the indoor condition signals from the four working modes, and after the classification process, sends a response request to the subsequent device. This part is implemented using a character finite state machine with four operating states (heating, cooling, dehumidification and no operation). In addition, in order to protect the subsequent devices, a protection mechanism for abnormal input is introduced in the design of the state machine, that is, when the device driver module determines that the abnormal input is input (for example, both indoor and outdoor conditions occur simultaneously), all device requests are immediately prohibited. . The state transition control relationship of the device driver module is shown in Figure 6.

Figure 6 output drive state transition diagram

6 Design verification

The design is described in the VHDL language with good portable characteristics. The FPGA/ACEX1K /EP1K30TC144-3 chip is used as the test carrier by Altera's MAX+PLUSII tool software, and the compiler test and hardware verification are carried out.

6.1 Simulation test

The overall simulation test results of the controller are as follows:

Figure 7 Controller Simulation Waveform 1

Figure 8 Controller Simulation Waveform 2

Figure 7 shows the response of the controller's button input. As shown in the figure, as the button is pressed, the various outputs are normal. Figure 8 shows the waveform of the controller operating in sleep mode with a wind speed of 4 and timing for two hours. It can be clearly seen from the figure that the STATE signal flashes when the shutdown comes, and the self-set temperature value also follows The time is increased from 21 ° C to 23 ° C. Based on the above analysis, it can be seen that the software simulation has achieved the expected performance indicators.

6.2 Resource usage status

FPGAs are precisely testable, and with powerful analysis software, accurate predictions and estimates can be made at the software design stage. According to the analysis of MAX+PLUSII software, the maximum delay of the critical path in the design is no more than 20 nanoseconds, which is not achieved by the general design method. The resource usage of the controller is shown in Table 1.

Table 1 Controller resource usage status

Input pin count output pin count logic unit number

15 32 230

6.3 Hardware Testing

The design passed the hardware test on the EDA technology development experimental platform of Leshan Teachers College in October 2007. The functions of the controller work normally, the whole machine runs well, the performance is stable, and the expected design index is achieved.

7 Conclusion

The introduction of FPGA technology has made the design get rid of the constraints of hardware circuits. Designers only need to put more effort into the design and optimization of software, which greatly improves the design efficiency. This design only lasted for more than two months from the task proposal to the final completion of the hardware test. This also proves to some extent the feasibility and great potential of introducing modern FPGA technology into the design of the air conditioner controller. With the continuous advancement of FPGA technology and its manufacturing process, it will be possible to integrate modern FPGA technology into the development and production of such controllers.

[references]

[1]http://xk.cn.yahoo.com/articles/070814/1/2a52_2.html. Yahoo Digital.

[2] Huang Zhiwei. FPGA system design and practice [M]. Beijing: Publishing House of Electronics Industry, 2005.

[3] Pan Song, Huang Jiye. EDA Technology and VHDL [M]. Beijing: Tsinghua University Press, 2005.

[4] Zhou Qi, Yan Zhaoliang. Current Status and Development Trend of Household Air Conditioners[J].Shanxi Architecture, 2007, (3): 159-160.

[5] AT89S51 datasheet http://

[6] EPCS1SI8 datasheet http://

[7] ST3 datasheet http://

[8] ST4 datasheet http://

:

October 23, 2023

August 16, 2023

January 16, 2024

អ៊ីម៉ែលទៅកាន់អ្នកផ្គត់ផ្គង់នេះ

October 23, 2023

August 16, 2023

January 16, 2024

សេចក្តីថ្លែងការណ៍សិទ្ធិឯកជន: ភាពឯកជនរបស់អ្នកមានសារៈសំខាន់ណាស់សម្រាប់យើង។ ក្រុមហ៊ុនរបស់យើងសន្យាថានឹងមិនបង្ហាញព័ត៌មានផ្ទាល់ខ្លួនរបស់អ្នកទៅប្រទេសនីន្នីណាមួយដែលមានការអនុញ្ញាតច្បាស់លាស់របស់អ្នកឡើយ។

បំពេញព័ត៌មានបន្ថែមដូច្នេះវាអាចទាក់ទងជាមួយអ្នកបានលឿនជាងមុន

សេចក្តីថ្លែងការណ៍សិទ្ធិឯកជន: ភាពឯកជនរបស់អ្នកមានសារៈសំខាន់ណាស់សម្រាប់យើង។ ក្រុមហ៊ុនរបស់យើងសន្យាថានឹងមិនបង្ហាញព័ត៌មានផ្ទាល់ខ្លួនរបស់អ្នកទៅប្រទេសនីន្នីណាមួយដែលមានការអនុញ្ញាតច្បាស់លាស់របស់អ្នកឡើយ។